## THÈSE DE DOCTORAT DE L'UNIVERSITÉ PSL

Préparée à MINES ParisTech

## Analyse et compilation de langages de programmation parallèle

Analysis and Compilation of Parallel Programming Languages

Soutenue par Adilla SUSUNGI Le 26 novembre 2018

École doctorale nº432 Sciences des métiers de l'ingénieur

## Spécialité

Informatique temps-réel, robotique et automatique

## Composition du jury :

| Gaétan HAINS<br>Professeur, Université Paris-Est Créteil  | Président             |

|-----------------------------------------------------------|-----------------------|

| Philippe CLAUSS<br>Professeur, Université de Strasbourg   | Rapporteur            |

| P. SADAYAPPAN<br>Professeur, Ohio State University        | Rapporteur            |

| Christine EISENBEIS<br>Directrice de recherche, Inria     | Examinateur           |

| Claude TADONKI<br>Directeur de recherche, MINES ParisTech | Directeur de thèse    |

| Albert COHEN<br>Directeur de recherche, Inria             | Co-directeur de thèse |

# Remerciements Acknowledgements

Je souhaiterais exprimer ma reconnaissance envers toute personne ayant contribué, de près ou de loin, à la complétion de cette thèse.

Je remercie tout d'abord François Irigoin de m'avoir accueillie au sein du centre de recherche en informatique (CRI) à Fontainebleau et de m'avoir donné l'opportunité de travailler sur le projet ACOPAL, financé par l'université Paris Sciences et Lettres.

Je ne prendrai jamais pour acquis le fait d'avoir été dirigée par Claude Tadonki et Albert Cohen. Tout le long de cette thèse vous m'avez impressionnée tant par votre expertise scientifique que par votre amabilité, votre sens de l'encouragement et votre intégrité.

Je remercie chaleureusement les membres de mon jury: Gaétan Hains ayant accepté de présider le jury, Philippe Clauss et P. Saday ayant rapporté mon manuscrit de thèse, Christine Eisenbeis ayant participé en tant qu'examinatrice, ainsi que Jeronimo Castrillon et Norman Rink, nos invités. I would like to particularly thank Jeronimo who gave me the opportunity to visit his lab, the Chair for Compiler Construction at TU Dresden, and collaborate with him and Norman. I owe half of this thesis work to our collaboration and, especially, Norman's investment and precious help. Also, thanks to Immo Huismann, Jörg Stiller and Jochen Fröhlich for providing access to their applications.

J'ai énormément de chance d'avoir été entourée par les membres du CRI (anciens ou actuels), c'est-à-dire, Corinne Ancourt, Arthur Aubertin, Maksim Berezov, Laila Bouhouch, Catherine Le Caër, Fabien Coelho, Laurent Daverio, Emilio Gallego, Guillaume Genestier, Florian Gouin, Pierre Guillou, Olfa Haggui, Olivier Hermant, Pierre Jouvelot, Patryk Kiepas, Nelson Lossing, Claire Medrala, Luc Perera, Benoît Pin, Bruno Sguerra, Lucas Sguerra, Pierre Wargnier et, bien que n'étant pas membre du CRI, je n'oublie certainement pas Monika Rakoczy; ils sont toujours prêts à aider si besoin (scientifiquement parlant ou de façon purement pratique) et sont tout simplement sympathiques, drôles, voire fous à lier ;-)

De par mes nombreuses visites à l'ENS, j'ai eu le plaisir de côtoyer Ulysse Beaugnon, Andi Drebes, Guillaume Iooss, Chandan Reddy, Oleksandr Zinenko et Jie Zhao. *My visit at the Chair for Compiler Construction also allowed me to meet great peers including Hasna Bouraoui, Sebastian Ertel, Andrés Goens, Fazal Hameed, Asif Ali Khan, Robert Khazanov, Nesrine Khouzami, Christian Menard and Lars Schütze.*

Enfin, merci à ma famille et mes amis d'avoir plus cru en moi que moi même.

# **Table of Contents**

| Та | ble o | of Contents                                                          | iii |

|----|-------|----------------------------------------------------------------------|-----|

| 1  | Intr  | roduction                                                            | 1   |

|    | 1.1   | Parallel Architectures, Programming Languages and Challenges         | 6   |

|    | 1.2   | Research Context                                                     | 9   |

|    | 1.3   | Thesis Contributions and Outline                                     | 12  |

| 2  | Inte  | ermediate Representation for Explicitly Parallel Programs: State-of- |     |

|    | the-  |                                                                      | 13  |

|    | 2.1   | Intermediate languages                                               | 14  |

|    | 2.2   | Program Representations Using Graphs                                 | 17  |

|    | 2.3   | The Static Single Assignment Form                                    | 21  |

|    | 2.4   | The Polyhedral Model                                                 | 22  |

|    | 2.5   | Discussion                                                           | 25  |

|    |       | 2.5.1 Observations                                                   | 25  |

|    |       | 2.5.2 Perspectives                                                   | 29  |

| 3  | The   | Tensor Challenge                                                     | 31  |

|    | 3.1   | Numerical Applications                                               | 32  |

|    | 3.2   | Computational Fluid Dynamics Applications: Overview                  | 33  |

|    | 3.3   | CFD-related Optimization Techniques                                  | 34  |

|    |       | 3.3.1 Algebraic Optimizations                                        | 35  |

|    |       | 3.3.2 Loop Transformations                                           | 37  |

|    | 3.4   | Envisioned Tool Flow                                                 | 39  |

|    | 3.5   | Existing Optimization Frameworks                                     | 40  |

|    |       | 3.5.1 Linear and Tensor Algebra Frameworks                           | 40  |

|    |       | 3.5.2 Levels of Expressiveness and Optimization Control              | 43  |

|    | 3.6   | Outcomes                                                             | 43  |

| 4  | The   | NUMA Challenge                                                       | 45  |

|    | 4.1   | NUMA Architectures: Topologies and Management Solutions              | 46  |

|    |       | 4.1.1 Operating Systems                                              | 46  |

|    |       | 4.1.2 NUMA APIs                                                      | 48  |

|   |      | 4.1.3   | Languages extensions                              |

|---|------|---------|---------------------------------------------------|

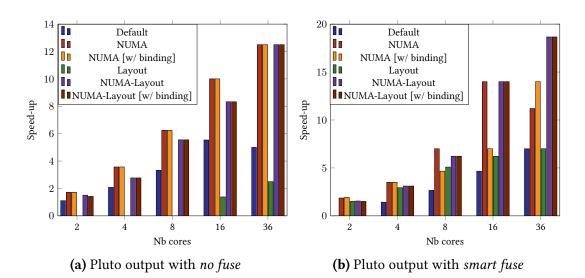

|   | 4.2  | Case S  | tudy: Beyond Loop Optimizations for Data Locality |

|   |      | 4.2.1   | Experimental Setup                                |

|   |      | 4.2.2   | Observations                                      |

|   | 4.3  | Refinir | ng NUMA Memory Allocation Policies                |

|   |      | 4.3.1   | Thread array regions and page granularity         |

|   |      | 4.3.2   | Implementation                                    |

|   |      | 4.3.3   | Limitations                                       |

|   | 4.4  | Data R  | eplications Implementation                        |

|   |      | 4.4.1   | Conditional Branching                             |

|   |      | 4.4.2   | Replication Storage    63                         |

|   | 4.5  | On Ru   | n-time Decisions                                  |

|   | 4.6  | Outcon  | mes                                               |

| 5 | TeN  | 1L: the | Tensor Optimizations Meta-language 67             |

|   | 5.1  | Overvi  | iew                                               |

|   | 5.2  | Tensor  | s                                                 |

|   |      | 5.2.1   | N-dimensional Arrays                              |

|   |      | 5.2.2   | Compute Expressions         73                    |

|   |      | 5.2.3   | Tensor Operations         74                      |

|   |      | 5.2.4   | Initializations                                   |

|   | 5.3  | Loop C  | Generation and Transformations    77              |

|   | 5.4  | Memo    | ry Allocations                                    |

|   | 5.5  | Implen  | nentation and Code Generation                     |

|   | 5.6  | On Da   | ta Dependencies                                   |

|   |      | 5.6.1   | Dependency Checks using Explicit Construct        |

|   |      | 5.6.2   | Decoupled Management                              |

|   | 5.7  | Evalua  | tion                                              |

|   |      | 5.7.1   | Expressing Tensor Computations                    |

|   |      | 5.7.2   | Reproducing Loop Optimization Paths               |

|   |      | 5.7.3   | Performance                                       |

|   | 5.8  | Conclu  | usion                                             |

| 6 | Form | nal Spe | cification of TEML 95                             |

|   | 6.1  | Forma   | l specification                                   |

|   |      | 6.1.1   | Domains of trees                                  |

|   |      | 6.1.2   | State                                             |

|   |      | 6.1.3   | Valuation functions    97                         |

|   | 6.2  | Compo   | ositional definitions                             |

|   |      | 6.2.1   | Loop transformations                              |

|   |      | 6.2.2   | Tensor operations                                 |

|   | 6.3  | Range   | Inference                                         |

## **Table of Contents**

|    |       | Towards Type SafetyConclusion                       |     |

|----|-------|-----------------------------------------------------|-----|

| 7  | Con   | aclusion and Perspectives                           | 115 |

| Bi | bliog | raphy                                               | 119 |

| A  | ICC   | Optimizations Reports                               | i   |

|    | A.1   | Naive Interpolation                                 | i   |

|    | A.2   | Naive Interpolation with Loop-invariant Code Motion | v   |

## Chapter 1

## Introduction

### Traduction en Français

La puissance des architectures parallèles ne cesse de croître depuis leur apparition ; les supercalculateurs les mieux classés ces dernières années illustrent bien cette tendance. En effet, les performances maximales pour *ASCI Red* (1998), *Roadrunner* (2008) et *Summit* (2018) sont respectivement de l'ordre des teraFLOPS, petaFLOPS et exaFLOPS. Cette différence notable peut s'expliquer par deux principaux facteurs. Premièrement, de plus en plus de cœurs sont intégrés afin d'offrir plus de parallélisme : 9 152 cœurs pour *ASCI Red*, 129 600 cœurs pour *Roadrunner* et 2 282 544 cœurs pour *Summit*. Deuxièmement, divers aspects liés au matériel (incluant la hiérarchie de la mémoire, la capacité de stockage et les interconnexions) sont améliorés ; par exemple l'ordonnancement des threads, les instructions vectorielles ou la gestion de la mémoire.

Un tel potentiel de puissance de calcul vient au prix d'une conception de plus en plus complexe et parfois difficile à appréhender. Il est pourtant nécessaire de comprendre ces architectures afin de les exploiter. Un premier pas vers cette compréhension est la reconnaissance des différents types modèles mémoires pouvant composer une architecture parallèle. Dans les *systèmes à mémoire partagée*, les cœurs partagent généralement le même espace mémoire. En revanche, les *systèmes à mémoire distribuée* sont des grappes de machines reliées par le réseau, où chaque machine possède sa propre mémoire. Ainsi, l'accès à des données situées sur des machines distantes n'est possible que si des communications explicites sont instanciées. Dans le contexte du calcul accélérée, un système *hétérogène* comprend des processeurs manycore tels que les GPUs et les FPGAs contrôlés à partir d'une machine standard (l'hôte) via un bus PCI.

De plus, certaines architectures peuvent être intrinsèquement hétérogènes. Par exemple, ARM big.LITTLE associe des cœurs de processeurs économes et lents avec des cœurs rapides à forte consommation. D'autres exemples sont les APU AMD qui combinent des processeurs multicœurs et un processeur graphique sur une seule puce.

En fonction du type de système ciblé, différents langages de programmation parallèle et APIs doivent être utilisés. OpenMP [9], Pthreads [12] ou Cilk [6] ont d'abord été conçus pour

les systèmes à mémoire partagée, MPI [7] pour les systèmes à mémoire distribuée et CUDA [2] ou OpenCL [8] pour les accélérateurs. En outre, les superordinateurs étant généralement des grappes de processeurs combinées à des accélérateurs, il est courant de combiner des langages en fonction des types de modèles mémoires présents (par exemple, OpenMP + CUDA, MPI + Pthreads, etc). Cependant, une autre tendance est également d'apporter plus de transparence dans la programmation hétérogène avec des extensions de langage (par exemple, le support du calcul accélérée dans OpenMP 4.0 ou encore l'introduction de communications unilatérales dans MPI 3.0). Une autre alternative est l'introduction du modèle PGAS (*Partitioned Global Access Space* ou encore "modèle de mémoire partagée distribuée"). Dans ce type de modèle de mémoire, la mémoire partagée est partitionnée de manière logique afin que différents threads aient leur propre espace d'adressage. Les nouveaux langages tels que X10 [15], Chapel [1] ou UPC [14] suivent le modèle PGAS.

La programmation parallèle peut être néanmoins difficile. En effet, plusieurs problèmes inhérents au parallélisme existent.

#### Les data races

Survenant lorsque, sans synchronisation appropriée, différents threads accèdent au même emplacement de mémoire et, sur au moins un de ces accès, une écriture est effectuée. Ceci entraîne des résultats inexacts. Cependant, certaines *data races* peuvent être délibérées : celles-ci sont dites bénignes.

#### Les deadlocks

On parle de deadlock lorsqu'un thread attend un événement qui ne se produira jamais ou lorsque deux threads s'attendent simultanément. Par conséquent, le programme ne se termine jamais. Cela peut se produire tant bien dans le modèle de mémoire partagée que dans le modèle de mémoire distribuée.

#### Les synchronisations

Une mauvaise gestion des synchronisations de threads nuit aux performances. Par exemple, des sections critiques avec trop de charge de travail impliquent l'attente de threads. Le temps d'inactivité de threads qui attendent trop longtemps doit donc être réduit.

#### Les faux partages

Les faux partages (*false sharing*) sont inhérents aux systèmes à mémoire partagée avec une cohérence de cache trop conservatrice (notamment celle basées sur les protocoles MESI ou MOESI). Ils se produisent lorsque plusieurs cœurs partagent la même ligne de cache. En effet, une ligne de cache partagée est invalidée chaque fois qu'il y a une écriture. Par conséquent,

les autres threads lisant leurs données doivent récupérer fréquemment la ligne de cache, ce qui dégrade les performances.

#### Localité de données et latences de transferts

Les latences de transferts se produisent à différentes échelles. Nous pourrions par exemple distinguer les communications entre processus dans un modèle de mémoire distribuée (ou hétérogène) des transferts de données standard au sein d'un système à mémoire partagée. Nous pourrions encore distinguer les transferts à l'échelle du registre vectoriel dans les architectures SIMD. Cependant le principe reste le même ; une mauvaise localité des données implique des latences de transfert plus élevées.

#### Les goulots d'étranglement

Les goulots d'étranglement surviennent lorsque trop de threads accèdent à la même mémoire, saturant ainsi le bus de communication. Il s'agit d'un facteur spécifique de latences de transferts élevées, typiques des applications ne tenant pas compte des architectures NUMA (*Non-Uniform Memory Access*).

#### Contexte de recherche

Relever les défis du parallélisme nécessite une connaissance approfondie de divers aspects liés au programme à optimiser ainsi que l'architecture sous-jacente.

Premièrement, l'algorithme en question pourrait être modifié afin d'exposer le parallélisme et améliorer l'efficacité des accès mémoires. Dans certains cas, une programmation parallèle inefficace provient d'un manque de connaissance du langage de programmation utilisé. Par exemple, une utilisation incorrecte des constructeurs de synchronisation entraîne une exécution incorrecte du programme (éventuellement provoquée par des data races).

Deuxièmement, les différents types de systèmes décrits au préalable peuvent impliquer différents types de stratégies pour exploiter pleinement leur potentiel. Par conséquent, il peut être difficile d'optimiser une application s'exécutant sur un cluster hétérogène. En outre, nous devons non seulement étudier quelle transformation de programme est adéquate sur une architecture donnée, mais nous avons également parfois besoin d'une connaissance approfondie de certains langages de programmation pour tirer le meilleur parti du matériel. Un exemple typique est CUDA, spécialement conçu pour les GPU NVIDIA : son abstraction de bas niveau peut augmenter la courbe d'apprentissage. Par conséquent, une programmation efficace sur des architectures hétérogènes implique un large éventail de connaissances qu'un programmeur doit posséder.

Les compilateurs sont des outils dont le flux est souvent caractérisé par (i) l'analyse d'un code source et sa traduction en une (ou plusieurs) représentation(s) intermédiaire(s), (ii) l'application de différentes techniques de transformation pour optimiser le programme et (iii) la traduction de la version optimisée du code en code assembleur (compilation traditionnelle) ou en un code source de haut niveau (compilation source-à-source). L'application de transformations sur les représentations intermédiaires afin d'optimiser le programme implique que l'analyse et la vérification du programme font également partie du processus. Par conséquent, les compilateurs peuvent aider à alléger la tâche d'un programmeur en prenant en charge une partie de tout le refactoring de code nécessaire pour utiliser efficacement l'architecture cible.

Malheureusement, les technologies de compilation actuelles ne semblent pas répondre aux besoins de la compilation parallèle. En effet, leurs *représentations intermédiaires* (RI), qui sont des clés pour effectuer des optimisations, ont été originellement conçues pour des programmes séquentiels uniquement. Cela ne restreint pas la possibilité de compiler des programmes parallèles car les constructions parallèles sont traduites en appels runtime. Mais certaines limitations persistent:

- Les représentations intermédiaires n'intègrent pas la sémantique des constructeurs parallèles. Sans sémantique parallèle, les RIs ont une expressivité restreinte pour adapter les techniques d'optimisation courantes aux programmes parallèles et permettre des techniques spécifiques au parallélisme. Par exemple, comment un compilateur peut-il analyser les instances de synchronisation pour éviter des data races si sa RI ne contient aucune abstraction des synchronisations ?

- 2. Les appels runtime empêchent l'application de techniques d'optimisations classiques sur les parties séquentielles d'un programme parallèle. Comme le compilateur ne connaît pas les effets secondaires de ces appels d'exécution, il abandonne tout choix d'optimisation. Même les compilateurs pour les programmes parallèles usent d'appels runtime, comme en est le cas du compilateur Chapel qui traduit le code source en C ou C ++ avec des appels runtime.

Par conséquent,

# Comment pourrions-nous repenser la conception des représentations intermédiaires pour les architectures parallèles?

#### Contributions de cette thèse

Cette thèse contribue à divers aspects liés aux représentations intermédiaires pour les architectures parallèles, dans le cadre de la compilation statique. Elle inclue :

- 1. un état de l'art des représentations intermédiaires parallèles ;

- 2. la conception, l'implémentation et la formalisation de TEML, un méta-langage pour l'optimisation d'applications tensorielles, à la lumière des perspectives de recherche exposées par l'état de l'art.

## Publications

Les travaux de cette thèse ont conduit à plusieurs publications (et une soumission en cours d'évaluation) sur lesquelles certaines parties de ce manuscrit sont basées, voire sont des extraits.

#### Journaux

**A. Susungi**, C. Tadonki. Intermediate Representations for Explicitly Parallel Programs. Submitted to *ACM Computing Surveys* in November 2018.

#### **Conférences internationales**

**A. Susungi**, N. A. Rink, A. Cohen, J. Castrillón, C. Tadonki. Meta-programming for cross-domain tensor optimizations. In Proceedings of *Generative Programming: Concepts & Experiences (GPCE)*, Boston, November 2018.

**A. Susungi**. On the Semantics of Loop Transformation Languages (Extended abstract). In Proceedings of 2nd International Conference on the Art, Science, and Engineering of Programming (<Programming'18> Companion), Nice, April 2018.

**A. Susungi**, N. A. Rink, J. Castrillón, I. Huismann, A. Cohen, C. Tadonki, J. Stiller, J. Fröhlich. Towards Generative and Compositional Tensor Optimizations (Short paper). In Proceedings of *Generative Programming: Concepts & Experiences (GPCE)*, Vancouver, October 2017.

#### Workshop internationaux

N. A. Rink, I. Huismann, **A. Susungi**, J. Castrillón, J. Stiller, J. Fröhlich, C. Tadonki, A. Cohen. CFDlang: High-level Code Generation for High-Order Methods in Fluid Dynamics. In Proceedings of *International Workshop on Real World Domain-specific Languages (RWDSL)*, Vienna, February 2018.

**A. Susungi**, A. Cohen, C. Tadonki. More Data Locality for Static Control Programs on NUMA Architectures. In Proceedings of *International Workshop on Polyhedral Compilation Techniques (IMPACT)*, Stockholm, January 2017.

\* 🜲 \* 🜲 \*

## 1.1 Parallel Architectures, Programming Languages and Challenges

The power of parallel architectures has been ever increasing since their emergence and topranked supercomputers in these last years illustrate this trend. The order of magnitude of peak performances for *ASCI Red* (1998), *Roadrunner* (2008) and *Summit* (2018) are respectively teraFLOPS, petaFLOPS and exaFLOPS. Such differences every decade can be explained by two main factors. First, more and more cores are integrated for greater parallelism: 9,152 cores for *ASCI Red*, 129,600 cores for *Roadrunner* and 2,282,544 cores for *Summit*. Second, hardware organization (including memory hierarchy, storage capacity, and interconnections) is revisited to improve various aspects such as thread scheduling, vector instructions, and memory management. The potential of recent hardware comes along with a more complex design that can be difficult to grasp, but necessary to understand to leverage them.

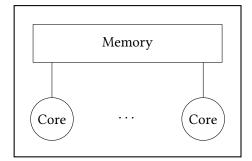

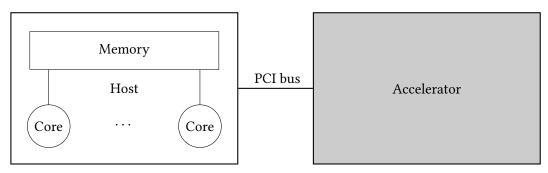

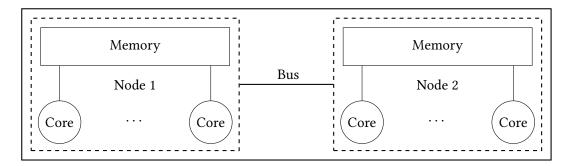

The first step towards understanding is acknowledging the different types of memory systems composing a parallel architecture (cf. Figure 1.1). In *shared memory systems*, cores share the same memory and addressing space. On the other hand, *distributed memory systems* are clusters of machines linked through the network where each machine has its own private memory. Thus, accesses to data located on remote machines require the instantiation of explicit communications. In the context of accelerated computing, *heterogeneous* systems include manycore processors such as GPUs and FPGAs monitored from a standard machine (the host) through a PCI bus.

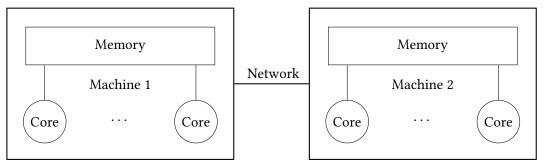

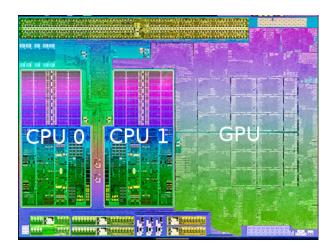

Heterogeneity can be inherent to certain architectures. For instance, the ARM big.LITTLE (cf. Figure 1.2) couples slow processor cores with high-speed cores. Other examples are AMD APUs that combine multi-core processors and a GPU on a single chip (cf. Figure 1.3).

Different parallel programming languages and APIs are used, depending on the targeted system. OpenMP [9], Pthreads [12] or Cilk [6] were first designed for shared memory systems, MPI [7] for distributed memory systems and CUDA [2] or OpenCL [8] for accelerators. Furthermore, as supercomputers are clusters of CPUs combined with accelerators, it is common to combine languages targeting different memory systems (i.e. OpenMP + CUDA, MPI + Pthreads, etc). Though, another trend is to offer more transparency in heterogeneous programming with language extensions (i.e. support of accelerated computing in OpenMP 4.0, the introduction of one-sided communications in MPI 3.0). Another alternative is the introduction of the PGAS model (also known as "distributed-shared memory model"). This type of memory model is based on a logical partitioning of the shared memory so that different threads have their own addressing space. New languages such as X10 [15], Chapel [1] or UPC [14] follow the PGAS model.

Due to various issues inherent to parallelism, parallel programming can be challenging.

(a) Shared memory system

(b) Distributed memory system

(c) Heterogeneous memory system

Figure 1.1: Different types of memory systems in parallel architectures

Figure 1.2: ARM big.LITTLE

Figure 1.3: AMD Trinity APU die shot

#### Data races

Data races occur when, without proper synchronizations, different threads access to the same memory location and at least on these accesses is a write. These lead to inaccurate results. Nevertheless, *benign data races* are to be distinguished as they are deliberate.

#### Deadlocks

Deadlocks, that lead to programs that never terminates, can be created in different circumstances, e.g. a thread waiting for an event that will never occur, or two threads waiting for each other to complete their tasks. Deadlocks can be encountered in the shared memory model as well as in the distributed memory model.

#### Synchronizations

An improper use of synchronization constructs can lead to poor performances. For example, critical sections containing too much workload can result into thread stalling.

#### False sharing

Inherent to shared memory systems with too conservative cache coherence (especially when based on MESI or MOESI protocols), it occurs when several cores share the same cache line. The shared cache line is invalidated whenever one of the cores writes to it. Therefore, other threads reading their data need to re-fetch the cache line. Frequent data re-fetching degrades performances.

#### Data locality, transfer latencies

Poor data locality can increase transfer latencies and the number of memory accesses. These issues can happen at different scales; we can distinguish communications between processes in a distributed memory or a heterogeneous model from standard data transfer within a shared memory system, and even from transfers at the vector register scale in SIMD architectures.

#### Traffic contention

Traffic contention occurs when too many threads access the same memory, thus creating a bus bottleneck. This is a specific factor of high transfer latencies typical to NUMA-unaware applications.

## **1.2 Research Context**

Tackling parallel-specific challenges requires a deep knowledge of aspects related to the program as well as the underlying architecture. First, the program's algorithm may need to be rewritten to expose parallelism and enhance efficient memory accesses. In some cases, such rewriting can target the proper use of the parallel programming language. For instance, improper use of synchronization constructs when necessary leads to incorrect program execution (sometimes caused by data races or deadlocks). Second, the different types of systems depicted above may require different types of strategies to leverage their potential. Consequently, it can be challenging to optimize an application running on a heterogeneous cluster. Furthermore, not only should we investigate which program transformations are adequate on a given architecture, but we also sometimes need a good knowledge of certain programming languages to make the most of the hardware. A typical example is CUDA that is designed for NVIDIA GPUs; its low-level abstraction can increase one's learning curve. Therefore, efficient programming on heterogeneous architectures involves a wide spectrum of knowledge that a programmer needs to grasp.

Compilers are tools which flow is often characterized by (i) parsing a source language and translating it into an (or several) intermediate representation(s) (IR), (ii) applying various transformation techniques on the IRs to optimize the program then (iii) translating the optimized version of the code either into assembly code (traditional compilation) or a high-level program (source-to-source compilation). IR transformations to optimize the program implies that program analysis and verification are also part of the compilation process. Therefore, compilers can help alleviate a programmer's task by taking in charge part of all the code refactoring required for an efficient use of the target architecture.

Unfortunately, current compiler technologies seem not to catch up with the needs of parallel compilation. Indeed, their *intermediate representations*, that are keys to perform optimizations, were originally designed for sequential programs only. This does not restrain the possibility of compiling parallel programs since parallel constructs are translated to runtime calls. But such characteristics raise some limitations:

- 1. Intermediate representations do not integrate the semantics of parallel constructs. Therefore, it is difficult to adapt existing optimization techniques to parallel programs. This also limits the ability to apply parallel-specific techniques. For instance, how could a compiler analyze synchronization instances to avoid data races if its IR does not have any representation of synchronizations?

- 2. Runtime calls impede the application of common optimizations on sequential parts in a parallel program; with unknown side-effects of a runtime call, the compiler becomes conservative. For example, in Figure 1.4, constant propagation and dead store elimination are, as expected, applied when no MPI communications are used. However, Figure 1.5 shows that none of these optimizations have been performed due to the presence of the MPI constructs. Even compilers for parallel programs may rely on runtime calls; this is the case for the Chapel compiler that translates the source code into C or C++ with runtime calls.

Therefore,

```

if (taskid == 0) {

taskid.0_6 = taskid;

1

1

if (taskid.0_6 == 1)

a = 0;

2

2

b = a;

goto <bb 3>;

3

3

}

else

4

4

else if (taskid == 1) {

goto <bb 4>;

5

5

a = 1;

<bb 3>:

6

6

b = 2;

# DEBUG a => 1

7

7

printf("%d\n", b);

8 # DEBUG b => 2

8

# DEBUG __fmt => "%d\n"

0

}

9

__printf_chk (1, "%d\n", 2);

10

```

**Figure 1.4:** Original code sample without MPI communications (left) and its corresponding GCC IR (right) after applying -O2 optimizations

```

if (taskid == 0) {

taskid.0_6 = taskid;

1

1

a = 0;

if (taskid.0_6 == 0)

2

2

goto <bb 3>;

b = a;

3

3

MPI_Recv(&a, 1, MPI_INT, 1, 0,

4

else

4

goto <bb 4>;

→ MPI_COMM_WORLD, NULL);

5

}

<bb 3>:

5

6

6

else if (taskid == 1) {

7

a = 0;

7

a = 1;

8

b = 0;

MPI_Recv (&a, 1, 1275069445, 1, 0,

8

b = 2;

9

printf("%d\n", b);

9

↔ 1140850688, 0B);

MPI_Send(&b, 1, MPI_INT, 0, 0,

goto <bb 6>;

10

10

<bb 4>:

\hookrightarrow MPI_COMM_WORLD);

11

if (taskid.0_6 == 1)

}

11

12

goto <bb 5>;

13

else

14

goto <bb 6>;

15

<bb 5>:

16

a = 1;

17

b = 2;

18

# DEBUG __fmt => "%d\n"

19

__printf_chk (1, "%d\n", 2);

20

MPI_Send (&b, 1, 1275069445, 0, 0,

21

\hookrightarrow 1140850688);

```

**Figure 1.5:** Original code sample with MPI communications (left) and its corresponding GCC IR (right) after applying -O2 optimizations

How do rethink intermediate representation design for parallel architectures?

## 1.3 Thesis Contributions and Outline

This thesis contributes to various aspects related to the intermediate representation for static parallel source-to-source compilation:

- 1. A survey of parallel intermediate representations;

- 2. The design, implementation, and formalization of TEML, a tensor optimization metalanguage, in the light of research perspectives exposed by the survey.

We focus on expressiveness and functionality, thereby providing a flexible framework for suitable static optimizations, as well as prospective dynamic ones. This document is outlined as follows. Chapter 2 is a survey of contributions to parallel intermediate representations. Chapter 3 recalls characteristics of numerical applications and exposes challenges in tensor optimizations with, as an example, issues encountered in computational fluid dynamics. We then study the challenges of code transformations in the context of NUMA architectures in Chapter 4. Chapter 3 and 4 are preliminary to understand choices in the design of TEML, presented in Chapter 5. Chapter 6 presents the formal specification TEML. We then conclude this dissertation with Chapter 7, mentioning future work.

## Chapter 2

# Intermediate Representation for Explicitly Parallel Programs: State-of-the-art

Dans ce chapitre, nous étudions les représentations intermédiaires parallèles proposées ces dernières années. Contrairement à l'état-de-l'art proposé par Belwal et Surdashan [31], nous nous concentrons exclusivement sur les représentations de programmes explicitement parallèles. Nous prenons donc en compte un nombre considérable de contributions non incluses dans [31].

Les contributions sont classées en 4 catégories de représentations : les langages intermédiaires, les graphes, la forme d'assignation unique statique (SSA) et la représentation polyédrique. Ces différents types de représentations ont des rôles complémentaires dans un flot de compilation. En effet, les graphes sont utiles pour représenter, par exemples, différents attributs du flot d'un programme (par exemple le flux parallèle ou les dépendances). La forme SSA facilite l'analyse et l'optimisation du flot de données. Le modèle polyédrique quant à lui est puissant pour analyser et optimiser les boucles imbriquées. Et finalement, les langages servent de portes d'entrées pour générer ces différentes représentations.

Les contributions aux RIs parallèles sont principalement axées sur l'inclusion de la sémantique parallèle dans ces différents types de représentations. Mais ce domaine de recherche en est encore à ses débuts, ce qui laisse plusieurs perspectives de recherches encore possibles tels que la prise en compte des hiérarchies mémoires, la possibilité d'analyser les pointeurs, l'expressivité des RIs relativement à différents domaines d'applications, leur intégration concrète dans les outils de compilation, les méthodologies d'optimisations impliquant leur usage, ainsi que le rôle de la compilation dynamique.

\* # \* # \*

In this chapter, we survey parallel intermediate representations (PIR) proposed in recent years in the context of static compilation. Unlike the survey proposed by Belwal and Surdashan [31], we focus exclusively on representations for explicitly parallel programs. We, therefore, take into account a considerable amount of contributions not included in [31]. Contributions are classified in 4 categories with complementary roles in a compilation flow: intermediate languages, graphs, static single assignment form, and polyhedral representation. Indeed, graphs are useful to represent different program behaviors (e.g the parallel flow or dependences), the static single assignment form eases data-flow analyses and optimization, the polyhedral model is powerful to analyze and optimize nested loops and finally, intermediate languages are gateways to generate these different representations.

In the following, we address each category with an introduction and related contributions.

## 2.1 Intermediate languages

14

Intermediate languages ease program analysis. The C language, for instance, is difficult to analyze for several reasons including its large set of constructs and the difficulty of defining its formal semantics. An intermediate language such as CIL [97] is more convenient as it is an analyzable subset of C with fewer keywords. Another interest is to serve as a common intermediate language for compilers that support multiple languages. We can mention PIPS IR [10], designed for C and Fortran programs.

In the context of parallel programs, several intermediate languages have been proposed at different levels of abstraction. The main interest in designing such a language is to capture parallel semantics including expressing parallel loops, describing variables properties (e.g., shared or private) or abstract synchronizations.

#### Selected contributions in the literature

*Erbium* Miranda et al. [93, 92] proposed Erbium, an intermediate language specifically designed to support classic or platform-specific optimizations for streaming applications. Erbium features data structures and functions for the representation of data streaming and resource management.

Threads creation are abstracted as *processes* communicating and synchronizing through *event records*. Records abstract FIFO channels with read or write *views*, that is, unbounded streams addressable through non-negative indexes. Live elements of read or write views are stored in a *sliding window*. The size of such a window is a view's *horizon*.

Several primitives are useful for the management of resources: *commit, update, release* and *stall.* The following producer-consumer flow illustrates their usage. On a producer's side, a view is on read and write access until the producer *commits* it; at this point, the view becomes read-only and is made available to the consumer process. However, unless the consumer *updates* its view with the corresponding index, it will not actually consume the view. After being consumed, a view can be *released* and the storage location of the released view can be reused by a producer when using the *stall* primitive.

Erbium has been implemented in an experimental branch of GCC 4.3.

*GCC IR* In order to adapt GCC optimizations to parallel programs, one could think of reimplementing optimization passes. However, Pop and Cohen [104] attempt to tackle the lack of parallel semantics in GCC by preserving both parallel semantics and optimizations passes implementation. For this purpose, they propose a set of annotations.

*Dataflow annotations* abstract informations about accessed variables within a block such as read, write or reduced variables. *Control-flow annotations* abstract barriers and synchronizations (e.g, execution by a single thread, barrier, synchronization point, memory flush). Finally, *user hints* store any information provided by the programmer, including the schedule of a loop or the number of threads. These annotations characterize a parallel region through calls to factitious built-in functions in conditional statements.

Pragma-based programming languages such as OpenMP or HMPP could benefit from such abstractions.

**PLASMA IR** PLASMA [99] is a programming framework for writing portable SIMD programs. Supporting multiple types of high-level programming languages, its main component is the intermediate representation (PLASMA IR). Abstractions are provided for programs to be compiled to different SIMD architectures including accelerators or processors with SIMD extension.

The IR has four main categories of constructs: operators, vectors, distributors and vector compositions. *Operators* act on either primitive types (e.g add, multiply elements) or aggregations of primitive types called blocks (e.g permute blocks, retrieve maximum or minimum). *Vectors* are blocks with a length attribute. *Distributors* are parallel operations performed on vectors (e.g parallel addition of vectors, reduction of elements in a vector). Finally, *vector composition* allow the encoding of operations such as concatenation, slicing or gathering.

The input source file is a PLASMA source, written independently of any SIMD device and the generated code targets CPUs and NVIDIA GPUs. General loop transformations (e.g, loop fusion, tiling [138, 75]), communication optimizations or more specific GPU optimizations (e.g, memory coalescing [59]) can be performed within the IR.

**PENCIL** Baghdadi et al. designed PENCIL [24, 25], a portable intermediate language to ease highly optimized GPU code generation, lowered from domain-specific languages (DSLs). PENCIL extends a subset of C99 with specific constructs including directives, function attributes, and built-in functions. Pointer manipulation as arguments of functions is not allowed, as well as recursive function calls. Furthermore, a **for** loop must have a single iterator, non-changing start and stop values within the loop and a constant increment.

The main constructs of PENCIL are:

- the *assume predicate* which guarantees that a boolean condition **e** is held whenever the control flow reaches the predicate,

- the *independant directive* which is a loop annotation indicating that a loop has no dependencies,

- summary functions that describe memory access patterns of functions in order to analyze memory footprints

- the *kill statement* that signals that a variable or an array element is dead at the point where the statement is called.

PENCIL is used in a polyhedral compilation flow that generates OpenCL code, using PPCG [137], for programs written in VOBLA [30], a DSL for linear algebra.

**PIR** Zhao and Sarkar [141] designed PIR for Habanero-Java [44]. Constructed from an abstract syntax tree (AST), PIR is a three-level IR. The high-level PIR (HPIR) is a tree, the Region Structure Tree, based on the syntax of Habanero-Java constructs (finish, async, isolated, foreach, forall) and more general ones such as for and while. When reaching the middle-level (MPIR) parallel constructs are lowered to async, finish and isolated; constructs that cannot be directly expressed become a combination of these, for instance foreach is translated to a for with an async body. Finally the low-level (LPIR) is alike a sequential flat IR where parallel constructs are expressed as runtime APIs.

The May Happen in Parallel (MHP) analysis [21] or parallel loop chunking in the presence of synchronizations [118] can be performed at the HPIR, whereas other analysis such as load elimination or data race detection can rather be performed at the MPIR.

*SPIRE* Unlike other IRs, Khaldi et al. [77] proposed a methodology to extend sequential IRs with parallel semantics. Named SPIRE (Sequential to Parallel Intermediate Representation Extension), it introduces a few key constructs that abstract execution, synchronization, data distribution, communications, and the memory model.

Data and task parallelism are respectively represented with the **parallel** and **spawn** construct. Reductions can be specified using **reduced**. Collective synchronizations are abstracted using **barrier**, whereas **atomic** is used for mutual exclusions. The **single** construct defines the sequential execution of statements within a spawned section. Furthermore, memory information can be specified for variables using **private**, **shared** or **pgas**. Communications and point-to-point synchronization are handled with intrinsic functions: **send()**, **recv()**, **signal()** and **wait()**.

A proof of concept is demonstrated with the generation of OpenMP task parallelism in PIPS [76] and the optimization of OpenSHMEM communications in LLVM [78].

**INSPIRE** INSPIRE [73] is the parallel IR of the Insieme<sup>1</sup> compiler infrastructure.

The parallel execution of instructions is modeled as a *job* cooperatively executed by a thread group. **pfor** is the main construct for work distribution. Data distribution within a group is performed using **redistribute**. Point-to-point communications can be specified using **channels**. In addition, several built-in functions are used for parallelism management.

#### 16

<sup>&</sup>lt;sup>1</sup>Insieme Compiler project from the University of Innsbruck: www.insieme-compiler.org

The functions getThreadID() and getNumThreads() respectively return the thread identification and the total number of threads. Threads are allowed to create sub-thread groups with spawn(), which can be merged using merge() or mergeAll().

Several contributions demonstrate the usability of INSPIRE; Insieme's runtime system [131], a framework for the implementation and optimization of MPI programs based on the Insieme compiler and runtime system [100].

## 2.2 Program Representations Using Graphs

As shown in the survey of Stanier and Watson [126], graphs are popular in modern compilers. One of the most common is the control flow graph (CFG) [23]. The CFG represents all possible paths of a program during its execution. Formally, it is a graph CFG = (V, E, Entry, Exit) where:

- *V* is a set of nodes representing *basic blocks* in the program;

- *E* is a set of edges representing sequential control flow in the program;

- and *Entry* and *Exit* are respectively nodes representing the entry and exit points of the program.

Basic blocks are sequences of instructions with no jumps, nor conditional branching. Conditional branches mark the end of a basic block with two outgoing edges representing the *true* of *false* paths. CFGs are useful for control- and data-flow analyses (e.g reaching definitions, available expression, liveness analysis) and optimizations (e.g, unreachable code elimination, common sub-expression elimination, copy or constant propagation) [22].

However, classic CFG properties are not sufficient for parallel programs. Indeed, the flow of parallel programs involves in addition concurrency, synchronization, mutual exclusion and sometimes, explicit communications. The wide implementation of the CFG in compilers and their unsuitability for parallel programs is the main motivations for contributions to provide adequate CFGs for parallel programs.

Another main representation is the program dependence graph (PDG) [64]. It is defined as a graph PDG = (V, E) where:

- *V* are nodes representing instructions;

- *E* either represent control or data dependences within the program.

Useful for dependence analyses, it can be applied to parallel programs if the parallel flow is properly captured. Figure 2.1 is an example of a program and its corresponding CFG and PDG.

#### Selected contributions in the literature

*Extended flow graph* Srinivasan and Wolfe [125] proposed the extended flow graph (EFG), a hierarchical representation combining parallel control flow graphs (PCFG) and parallel precedence graphs (PPG).

| 1 y = x<br>2 if (y<br>3 a = a<br>4 else<br>5 a = a<br>6 y += a | < 5)<br>+ 7;<br>- 7; | Entry $y = x$ $+ 7  if$ $(y < 5)$ $a = a + 7$ $a = a - 7$ $y + = a$ $Exit$ | y = x + 7<br>if $(y < 5)$<br>a = a + 7<br>y + = a |

|----------------------------------------------------------------|----------------------|----------------------------------------------------------------------------|---------------------------------------------------|

|                                                                |                      |                                                                            |                                                   |

Chapter 2. Intermediate Representation for Explicitly Parallel Programs: State-of-the-art

Figure 2.1: A program, its CFG (mid) and its PDG (left)

The PCFG is a graph  $G = (V_G, E_G, Entry_G, Exit_G)$  where:

- *V<sub>G</sub>* is a set of basic block nodes or parallel block (called *supernode*);

- $E_G$  is a set of edges representing potential flow of control in the program;

- *Entry*<sub>G</sub> is the unique start node;

- $Exit_G$  is the unique exit node.

Within a supernode, the parallel execution is represented by the PPG. The PPG is a graph  $P = (V_P, E_P, Entry_P, Exit_P)$  where:

- *V<sub>P</sub>* is a set of sections in a parallel block;

- *E<sub>P</sub>* is a set of *wait-dependence* arcs;

- *Entry*<sub>*P*</sub> is the co-begin node, where co-begin denotes the beginning of a parallel section;

- *Exit*<sub>P</sub> the co-end node, denoting the end of the parallel section.

Finally, each section in a parallel block is also represented by a PCFG  $S = (V_S, E_S, Entry_S, Exit_S)$  where  $Entry_S$  and  $Exit_S$  respectively represent the entry into and the exit from the section.

The PCFG comes along with a parallel SSA form presented in the next section.

**Parallel program graph** Sarkar and Simons [116] proposed the parallel program graph (PPG), a graph  $PPG = (N, E_{cont}, E_{sunc}, TYPE)$  where:

- *N* is a set of node representing arbitrary sequential computation;

- *E*<sub>cont</sub> are control edges;

- *E<sub>sync</sub>* are synchronization edges;

- *TYPE* is a node type mapping.

18

Nodes can be identified as: *START* (beginning of the program), *PREDICATE* (conditional statements, with two outgoing edges either *true* or *false*), *COMPUTE* (nodes with only one outgoing edge) and *MGOTO* (creation of a parallel section where each successor of the *MGOTO* node is a thread).

Authors demonstrate how the reaching definition analysis may be applied using the PPG [115]. However, such representation is restricted to deterministic parallel programs.

**Concurrent control flow graph** Lee et al. [84] proposed the concurrent control flow graph (CCFG). They introduce the notion of concurrent basic blocks (CBB) to incorporate thread interaction. A CBB has the fundamental definition of a basic block in a sequential program, but with three additional properties involving parallel program constructs: (*i*) only the *first* statement can be a **wait** or contain a use of a conflicting variable, (*ii*) only the *last* statement can be a **post** or contain a definition of a conflicting variable and (*iii*) if a CBB contains a parallel execution, a mutual exclusion construct or **barrier** statement, then that statement is the only one in the concurrent basic block except **end parallel do**.

A node that contains an **end parallel do** contains an assignment to the loop index variable.

Based on this, a CCFG is a directed graph G = (N, E, Ntype, Etype) where:

- *N* is the set of nodes representing basic blocks;

- *E* is the set of edges composed of control flow edges, synchronization edges and conflict edges;

- *Ntype* is a function telling the class of nodes;

- *Etype*, a function telling the type of edges.

The CCFG comes along with the concurrent SSA form presented in the next section.

**OpenMP control flow graph** Lin [85] introduced the OpenMP CFG (OMPCFG) to model control flow in OpenMP programs. The graphs is composed of: *basic nodes* for basic blocks and *directive nodes* for OpenMP directive blocks. *Entry* and *Exit* nodes are respectively the unique entry and exit points of the graph. The OMPCFG may serve for concurrency analysis and static data race detection.

**SPIR** Choi et al. [51] proposed the Signal Processing Intermediate Representation (SPIR), a dataflow graph for efficient mapping of streaming applications. It is graph G = (N, E) where:

- *N* is a set of nodes corresponding to either a task or the condition of an **if** statement;

- *E* are edges representing data transfer between tasks. Edges following **if** conditions are annotated with *true* or *false*.

A possible application is task mapping onto processors maximizing throughput under memory constraints.

*Kimble IR* Benoit and Louise [33] introduced the Kimble IR, meant to support explicit parallelism and perform automatic parallelization. It is a direct acyclic graph G = (N, D, E) where:

- *N* is a set of nodes corresponding to program constructs: function, loop, region, cluster (a sequence of dependent statements), statement, guard or function call;

- *D* is a set of ordered pairs of nodes denoting a dependency between two nodes;

- *E* is a set of ordered pairs of nodes expressing a hierarchical relationship.

Gomet [32], an extension of GCC to support multi-grain parallelism on MPSoCs uses Kimble IR. Program transformations such as reordering, function inlining and outlining can be performed within the IR. In [34], they describe how it is used to determine the execution cost on a given processor.

**MPI control flow graphs** The MPI-CFG [119] extends the CFD with communication nodes, which are separate basic blocks expressing communication statements, and edges denoting data transfer. Edges are also annotated with a value providing pieces of information about process IDs whenever possible. Additional information may be provided if such ID is unknown. An unknown process proven to be the only one executing a communication is annotated *single*. If one or more processes may be involved, *unknown* is the annotation. Finally, *multiple* may be used if it is guaranteed that more than one process executes the communication.

Point-to-point communications are typically abstracted using single communication edges. But specific representations have been provided for each type of collective communications such as broadcasting or scattering in order to reflect their unique semantics.

Strout et al. [129] demonstrate the MPI-CFG could be useful for static analysis. Furthermore, they propose the MPI-ICFG for inter-procedural MPI calls, obtained through an inter-procedural CFG [83] enhanced with communication edges.

**Delite IR** Delite [42] is a framework for the compilation of domain-specific languages to heterogeneous targets. Its IR is three-level.

The lowest level, the *generic* IR, is a composed of a collection of nodes only linked if their exist read-after-read or control dependencies; the nodes are free otherwise, hence named *sea of nodes*. The mid-level is the *parallel* IR, extending the generic IR to express particular parallelism patterns. For instance, a node with the label *sequential op* indicates that the node is executed sequentially and another one with a *reduce op* label indicates are reductions. Finally, since Delite's input programs can be written in various DSLs, the highest level is the *domain-specific* IR.

Different types of optimizations are performed depending on the level of IR. Domainspecific and parallel-specific optimization are respectively applied in the high-level and midlevel IR. Classic optimizations are mainly performed in the low-level IR.

20

**Tapir** Tapir [117] extended LLVM IR with fork-join parallelism. Using three instructions, that is, **detach**, **reattach** and **sync**, it extends the CFG to represent parallel task and synchronizations. Parallel loops are represented as spawned blocks into a number of tasks corresponding to the number of loop iterations.

A certain number of LLVM analyses and optimization passes have been adapted to Tapir including alias, data-flow analyses, and classic optimization passes.

## 2.3 The Static Single Assignment Form

The static single assignment (SSA) form [56] is a popular compilation technique that consists in assigning variables only once. That is, if a variable v is assigned 3 times, in the SSA form, each assignment will be uniquely identified as  $v_i$  with i = 1..3. When necessary to deal with control flow merges due to multiple possible paths (e.g after a **if-then-else** section), a  $\phi$ function is used to abstract merging points. For example, the SSA form of the code sample in Figure 2.1 is:

```

1 y1 = x1 + 7;

2 if (y1 < 5)

3 a2 = a1 + 7;

4 else

5 a3 = a1 - 7;

6 y2 = \phi(a2, a3);

```

The SSA form is often combined with the CFG as it eases the identification of data dependencies and thus enables more efficient data-flow optimization techniques. The SSA form cannot accurately be applied on array computations within loops. More accurate representations, *array* SSA forms, therefore exist [82, 114].

However, applying the SSA form in a parallel program exhibits issues: How do we handle merging points at the end of a parallel section? How do we handle the concurrent update of a shared variable within a task? Indeed, parallel sections may include writes by multiple threads on the same variable. As the order of thread execution may be non-deterministic, merging points at the end of such sections are necessary.

#### Selected contributions in the literature

Srinivasan et al. [124] pioneered parallel SSA (PSSA) forms. Their PSSA form features, in addition to the  $\phi$ -function, a  $\psi$ -function denoting parallel merge nodes. Nascent [128], a Fortran parallelizing compiler, uses the PSSA form for optimizations forward substitution and constant propagation in parallel programs. However, the PSSA form is limited to the PCF Fortran standard, with a weak memory consistency model.

For better generalization, Lee et al. [84] also proposed the concurrent SSA form (CSSA) similar to PSSA form but also capturing the update of a shared variable within a concurrent task using  $\pi$ -functions. They redefined a larger set of compiler analysis and optimizations

including copy propagation, dead code elimination, common sub-expression elimination, and redundant load/store elimination.

As the CSSA form focuses only on event-based synchronizations, Novillo et al. [98] proposed the CSSAME framework based on an extended CSSA form [84] to deal with mutual exclusion. The CSSAME framework does not introduce any new term; they incorporate the semantics of mutual exclusion synchronizations to be taken into account when building the CSSA form. They show how constant propagation, dead code elimination, and lock independent code motion can be performed in the presence of mutual exclusion.

Collard [55] aimed at representing accurately the array SSA form in the presence of concurrency, event-based synchronization or mutual exclusion. The idea is to clearly define the order of memory updates then applies array SSA form accordingly.

Chakrabarti and Banerjee [45] proposed an array SSA form in the context of the automatic generation of message-passing programs from a program similar to High-Performance Fortran standards. This work aims at maintaining accurate information about distributed data in such a context. Therefore, they not only distinguish merging at dominance frontier (through the  $\Phi_d$ -term) and after each non-killing write of an array (through the  $\Phi_w$ -term) but also before any read that occurs on a distributed array variable (through the  $\Phi_r$ -term). The array SSA form in an automatic parallelizing compiler named PARADIGM in order to perform data placement, generation and optimizations of data transfers for MPI final code generation.

## 2.4 The Polyhedral Model

The polyhedral model [63] is a mathematical representation of a subset of imperative languages called static control programs (SCoP). A SCoP is a maximal set of consecutive instructions where the loop bounds (**for** loops), conditions (**if** statements) and arrays (excluding pointers) are affine functions depending only on outer loop indexes (e.g, *i*, *j*) and constant parameters (e.g, *n*). Each statement *S* can be associated to an iteration vector  $x \in \mathbb{Z}^p$ , where the *i*<sup>th</sup> element of the vector is the loop index. The set of possible values for the iteration vector is called the *iteration domain*. The iteration domain can be therefore specified by a set of linear inequalities defining an integer polyhedron:

$$D_S = \{ \vec{x} \in \mathbb{Z}^p \mid A\vec{x} + \vec{c} > 0 \}$$

(2.1)

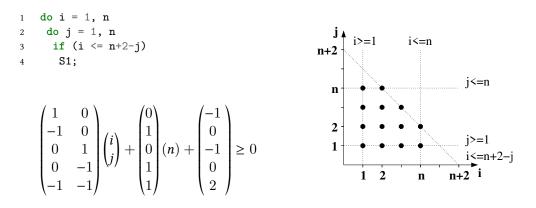

where  $\vec{x}$  is the iteration vector, *A* is a constant matrix and  $\vec{c}$  is a constant vector. Figure 2.2 illustrates the representation of a program in the polyhedral model.

Another characteristic of a SCoP is the *scheduling function* that describes the logical date of execution for each statement instance. For instance, given the following code sample where  $S_1$ ,  $S_2$  and  $S_3$  are instructions

**Figure 2.2:** A loop, its corresponding iteration domain (bottom left) and polyhedral representation (right).

1 for (i = 0; i < N; i++)

2 S1;

3 for (j = 0; j < N; j++)

4 S2;

5 S3:</pre>

the corresponding scheduling function is:

$$S_1(i) = (i, 0)$$

$S_2(i, j) = (i, 1, j, 0)$

$S_3(i, j) = (i, 1, j, 1)$

The polyhedral model enables exhaustive analysis of nested loops. Several state-of-the-art tools are based on polyhedral compilation techniques: Clan [16] or Pet [134] as extractors of the polyhedral representation of a program; isl [135] or PolyLib [87] as libraries for manipulating polyhedra; CLooG [27] as a polyhedral-to-C code generator; PPCG [137] as C-to-CUDA code generator.

Several compilers have integrated polyhedral compilation: PIPS [10], GCC through Graphite [106], LLVM through Polly [66], IBM XL through PluTo [38] and a R-stream [91].

Consequently, advances in parallelism support impact both research and industrial compilers.

#### Selected contributions in the literature

Contributions in the polyhedral model exhibit two approaches. Most researches attempt to identify at least subsets of parallel programs compatible with the polyhedral representation. However, extending the representation has also been addressed.

Basupalli et al. [28] integrated an OpenMP program verifier, OmpVerify, in the Eclipse IDE for data race detection. To perform such an analysis, they first extract the initial de-

pendences of the program (ignoring the parallel constructs), then they consider the parallel construct **omp for** as a program transformation that assigns new time-stamps to instances in the program. Finally, the task of the verifier is to ensure that this transformation does not introduce any data race. However, some dynamic concurrent accesses may be difficult to detect.

24

Liveness analysis for register allocation requires the computation of a set of conflicting variables in a live range. Such computation is based on the notion of total order among each iteration, which is not applicable to parallel programs. To put liveness analysis to work with parallel programs, Darte et al. [57] proposed a method where conflicting variables are computed based on the notion of partial order *and* the happens-before relationship that can be computed with Presburger sets and relations [136].

The Insieme compiler also features the translation from INSPIRE [73] to polyhedral representation. Therefore, Pellegrino et al. [101] developed a polyhedral-based approach to exact dependence analysis of MPI communications. They define, for MPI point-to-point and collective communications, semantically equivalent loops that fit in the polyhedral model. Communications must be first rewritten in a *normal form*, in which an MPI program only contains MPI\_Send and MPI\_Recv. Then a data dependence graph is generated in order to apply a set a transformation including loop fission or code motion.

In order to perform static data race detection in X10 programs, Yuki et al. [140] adapted the array dataflow analysis to a subset of the language, fitting in the polyhedral model. The subset includes sequences of instructions, sequential **for** loops, the parallel activation construct **async** and the termination construct **finish**. Similarly to [57] for liveness analysis, the array dataflow analysis is based on the happens-before relationship of instances.

Cohen et al. [52] studied polyhedral techniques applied to OpenStream [105], a stream-programming extension of OpenMP, mainly for static analyses such as dependence analysis and deadlock detection. The main idea is to exhibit the properties of OpenStream programs that can be represented in polyhedral analysis.

Unlike previous approaches, Chatarasi et al. [47] proposed extensions to the polyhedral model. They introduce the notion of *space mapping*, abstracting the multi-threaded loops and *phase mapping* to distinguish different parallel phases (e.g. separated by barriers). They demonstrate its usefulness for static data race detection.

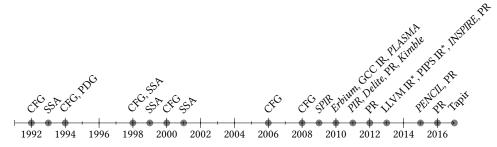

**Figure 2.3:** Timeline of attempts of revisiting existing IRs or designing new ones. IRs marked with \* are those that were extended with SPIRE. New IRs are in italic. PR stands for polyhedral representation

## 2.5 Discussion

Using further classifications, we may observe different trends in terms of language support, code generation, memory model or concrete application in compilers. Table 2.1 summarizes the different contributions, their year of appearance and the characteristics of the type of parallel programs supported.

#### 2.5.1 Observations

*Timeline.* Figure 2.3 exhibits two eras of parallel IR proposals; flow graphs and SSA forms prior to 2008, then from 2010 a variety of intermediate languages and extension of research compiler IRs.

*Language support* Most contributions target only one parallel language or a restricted set. PLASMA, SPIRE and INSPIRE are exception attempting to support a wider range of languages.

*Levels of abstractions for intermediate languages* We may generally consider that any contribution targeting GCC IR, LLVM IR or common graph representation are generalpurpose. However, Erbium, while being implemented in GCC, remains specific to streaming applications. On the other hand, PLASMA IR is architecture-specific.

Erbium and PENCIL, unlike other languages, may be used as user programming languages.

*IRs structure* PIR and Delite IR distinguished themselves with their multi-level IRs enabling various types of optimizations. With the complementarity of the CFG and SSA form, contributions of Srinivasan et al. [125, 124], and Lee et al. [84] can also be considered as multi-level IRs.

**Table 2.1:** Year of contributions and characteristics of their supported parallel programs

| Contributions                      | Characteristics of supported parallel programs           | Year |  |  |  |  |

|------------------------------------|----------------------------------------------------------|------|--|--|--|--|

|                                    | Intermediate languages                                   |      |  |  |  |  |

| [93] (Erbium)                      | Streaming applications                                   | 2010 |  |  |  |  |

| [99] (PLASMA IR)                   | SIMD parallelism                                         | 2010 |  |  |  |  |

| Рор, Сонем [105]                   | Directive-based                                          | 2011 |  |  |  |  |

| [141] (PIR)                        | Habanero-Java                                            | 2011 |  |  |  |  |

| [77] (SPIRE)                       | Multithreaded, distributed, PGAS                         | 2013 |  |  |  |  |

| [73] (INSPIRE)                     | Multithreaded, distributed, with accelerators            | 2013 |  |  |  |  |

| [24] (PENCIL)                      | DSLs                                                     | 2015 |  |  |  |  |

| [117] (Tapir)                      | Multithreaded                                            | 2017 |  |  |  |  |

|                                    | Graphs                                                   |      |  |  |  |  |

| [125] (EFG)                        | PCF Fortran                                              | 1992 |  |  |  |  |

| [116] (PPG)                        | Deterministic multithreaded                              | 1994 |  |  |  |  |

| [84] (CCFG)                        | Multithreaded                                            | 1998 |  |  |  |  |

| [119] (MPI-CFG)                    | MPI                                                      | 2000 |  |  |  |  |

| [129] (MPI-ICFG)                   | MPI                                                      | 2006 |  |  |  |  |

| [85] (OMPCFG)                      | OpenMP                                                   | 2008 |  |  |  |  |

| [51] (SPIR) Streaming applications |                                                          | 2009 |  |  |  |  |

| [32] (Kimble IR)                   | Multithreaded                                            |      |  |  |  |  |

| [42] (Delite IR)                   | DSLs                                                     | 2011 |  |  |  |  |

|                                    | SSA form                                                 |      |  |  |  |  |

| [124] (PSSA)                       | PCF Fortran                                              | 1993 |  |  |  |  |

| [84] (CSSA)                        | Multithreaded with event-based synchronizations          | 1998 |  |  |  |  |

| [98] (CSSAME)                      | Multithreaded with synchronizations and mutual exclusion | 1998 |  |  |  |  |

| [55]                               | Multithreaded with synchronizations and mutual exclusion | 1999 |  |  |  |  |

| [45]                               | HPF-like                                                 | 2001 |  |  |  |  |

|                                    | Polyhedral model                                         |      |  |  |  |  |

| [28]                               | OpenMP                                                   | 2011 |  |  |  |  |

| [101]                              | MPI                                                      | 2012 |  |  |  |  |

| [140]                              | X10                                                      | 2013 |  |  |  |  |

| [46]                               | Multithreaded                                            | 2015 |  |  |  |  |

| [47]                               | Multithreaded                                            | 2016 |  |  |  |  |

| [57]                               | Multithreaded                                            | 2016 |  |  |  |  |

| [52]                               | OpenStream [105]                                         | 2016 |  |  |  |  |

26

**Table 2.2:** Intermediate languages and some examples of their applications for language support, code generation and integration in compilers

| Intermediate languages Language support |                                | Code generation | Compilers              |

|-----------------------------------------|--------------------------------|-----------------|------------------------|

| [93] (Erbium) OpenStream [105]          |                                | -               | GCC [92]               |

| Pop and Cohen [105]                     | OpenMP, OpenACC                | -               | GCC                    |

| [99] (PLASMA IR)                        | OpenMP, Matlab, StreamIT       | CUDA            | PLASMA                 |

| [24] (PENCIL)                           | VOBLA [30]                     | OpenCL, CUDA    | DSL compilers          |

| [77] (SPIRE)                            | OpenMP, MPI, Chapel, OpenSHMEM | OpenMP          | LLVM [78], PIPS [76]   |

| [141] (PIR)                             | Habanero-Java [44]             | -               | Habanero-Java compiler |

| [73] (INSPIRE)                          | OpenMP, MPI, Cilk, OpenCL      | OpenMP, MPI     | Insieme [131, 100]     |

| <b>Table 2.3:</b> | IRs and | their | memory | model | ls scope |

|-------------------|---------|-------|--------|-------|----------|

|-------------------|---------|-------|--------|-------|----------|

| Contributions                 | Shared       | Distributed  | Host-accelerator | PGAS         |

|-------------------------------|--------------|--------------|------------------|--------------|

| [93] (Erbium)                 | $\checkmark$ |              |                  |              |

| Pop and Cohen [105]           | $\checkmark$ |              | $\checkmark$     |              |

| [99] (PLASMA IR)              | $\checkmark$ | $\checkmark$ | $\checkmark$     |              |

| [24] (PENCIL)                 |              |              | $\checkmark$     |              |

| [77] (SPIRE)                  | $\checkmark$ | $\checkmark$ |                  | $\checkmark$ |

| [73] (INSPIRE)                | $\checkmark$ | $\checkmark$ | $\checkmark$     |              |

| [117] (Tapir)                 | $\checkmark$ |              |                  |              |

| [125, 124] (EFG + PSSA)       | $\checkmark$ |              |                  |              |

| [84] (CCFG + CSSA)            | $\checkmark$ |              |                  |              |

| [116] (PPG)                   | $\checkmark$ |              |                  |              |

| [85] (OMPCFG)                 | $\checkmark$ |              |                  |              |

| [51] (SPIR)                   | $\checkmark$ |              |                  |              |

| [32] (Kimble IR)              | $\checkmark$ |              |                  |              |

| [119] (MPI-CFG)               |              | $\checkmark$ |                  |              |

| [129] (MPI-ICFG)              |              | $\checkmark$ |                  |              |

| [141] (PIR)                   |              |              |                  | $\checkmark$ |

| [42] (Delite IR)              |              |              | $\checkmark$     |              |

| [98] (CSSAME)                 | $\checkmark$ |              |                  |              |

| Collard [55]                  | $\checkmark$ |              |                  |              |

| Chakrabarti and Banerjee [45] |              | $\checkmark$ |                  |              |

| Basupalli et al. [28]         | $\checkmark$ |              |                  |              |

| Chatarasi et al. [47]         | $\checkmark$ |              |                  |              |

| Darte et al. [57]             | $\checkmark$ |              |                  |              |

| Pellegrini et al. [101]       |              | $\checkmark$ |                  |              |

| Yuki et al. [140]             | $\checkmark$ |              |                  |              |

| Cohen et al. [52]             | $\checkmark$ |              |                  |              |

Chapter 2. Intermediate Representation for Explicitly Parallel Programs: State-of-the-art

| Contributions                 | Analyses                            | Optimizations                     |  |

|-------------------------------|-------------------------------------|-----------------------------------|--|

| [125] (EFG + PSSA)            | N/A                                 | Constant propagation [128]        |  |

| [84] (CCFG + CSSA)            | Data-flow analyses                  | Redundant load/store elimination  |  |

| [116] (PPG)                   | Reaching definitions analysis [115] | N/A                               |  |

| [85] (OMPCFG)                 | Data race detection                 | N/A                               |  |

| [51] (SPIR)                   | Processor assignment                | Task scheduling                   |  |

| [32] (Kimble IR)              | Execution cost [34]                 | Function inlining/outlining       |  |

| [119] (MPI-CFG)               | N/A                                 | N/A                               |  |

| [129] (MPI-ICFG)              | Activity analysis                   | N/A                               |  |

| [141] (PIR)                   | May-happen-in-parallel analysis     | Dead code elimination             |  |

| [42] (Delite IR)              | Data-flow analyses                  | Pattern matching, domain-specific |  |

| [98] (CSSAME)                 | Detection of mutual exclusion       | Code motion                       |  |

| Collard [55]                  | N/A                                 | N/A                               |  |

| Chakrabarti and Banerjee [45] | Communication placement             | Communication optimization        |  |

| Basupalli et al. [28]         | Data race detection                 | N/A                               |  |

| Chatarasi et al. [46, 47]     | Data race detection                 | N/A                               |  |

| Darte et al. [57]             | Liveness analysis                   | N/A                               |  |

| Pellegrini et al. [101]       | Dependence analysis                 | Communication optimization        |  |

| Yuki et al. [140]             | Array data-flow analysis            | N/A                               |  |

| Cohen et al. [52]             | Deadlock detection                  | N/A                               |  |

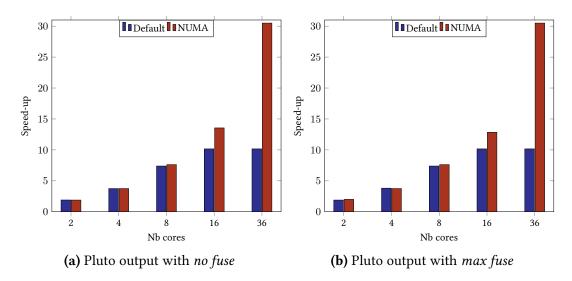

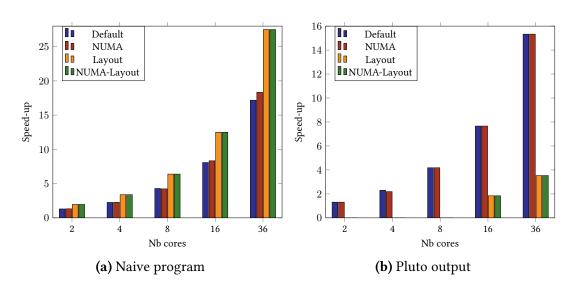

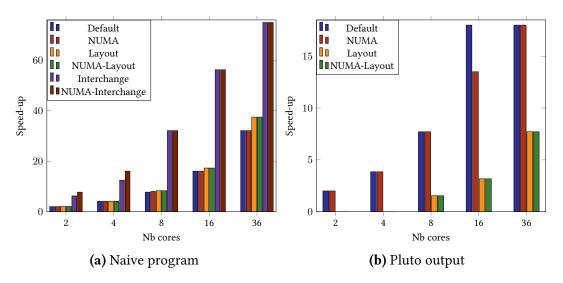

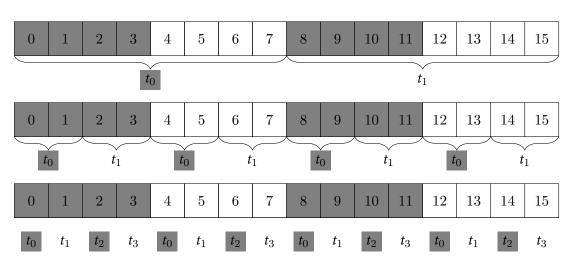

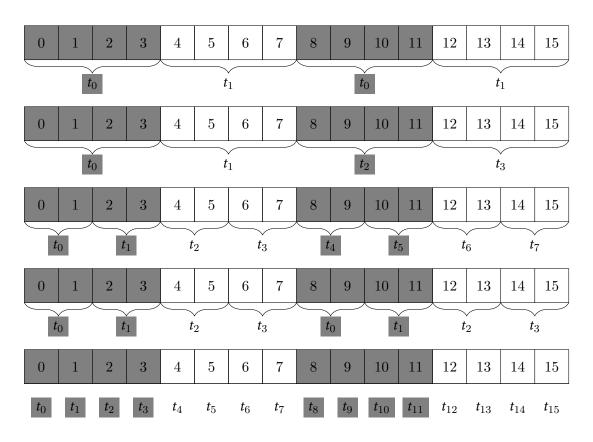

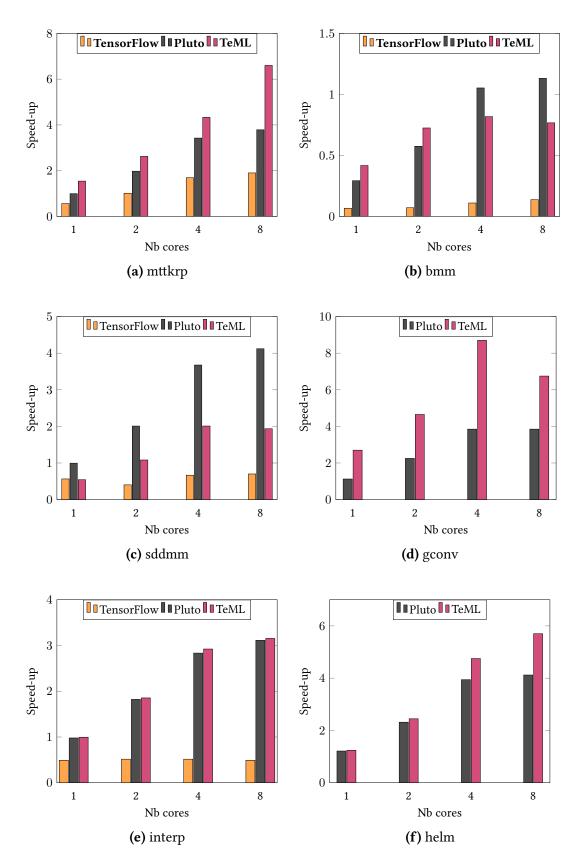

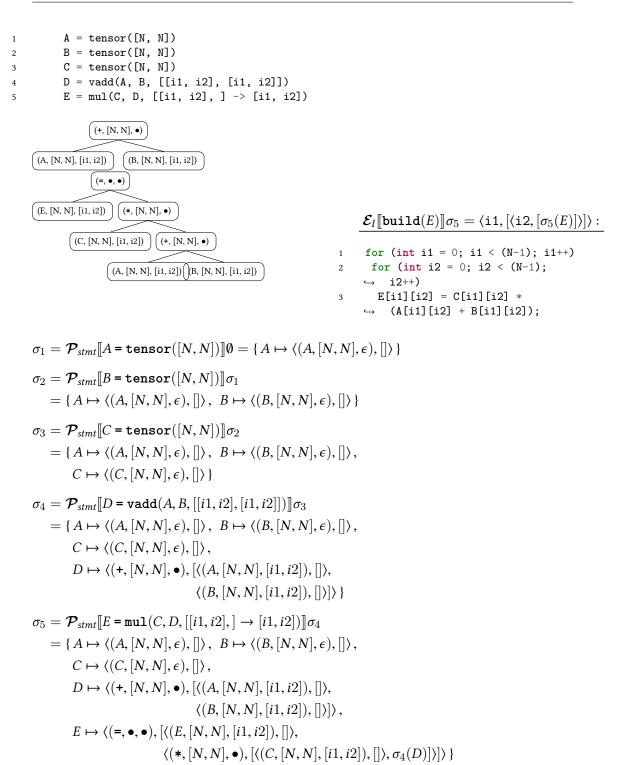

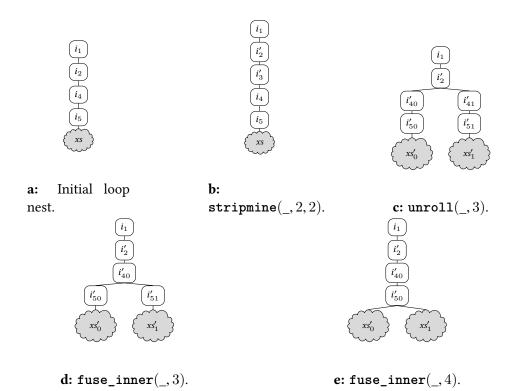

**Table 2.4:** Examples of applications for analyses/optimizations of graph-based IRs, parallel SSA forms and polyhedral model.